### Trends in HPC

Carlo Cavazzoni, CINECA

#### European HPC strategy

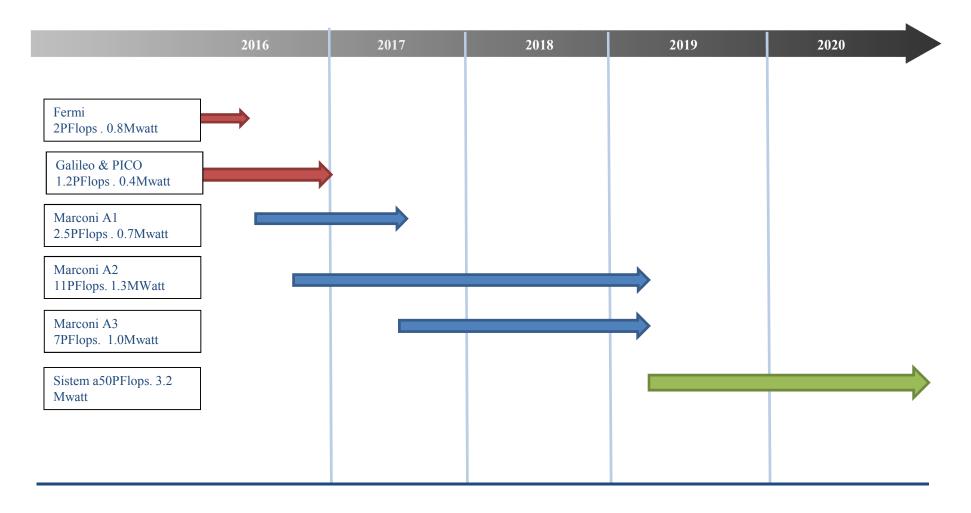

CINECA road map 2016-2021

#### 2016-2019 : Marconi

- > 18PFlop

- 100 racks

- 2.3MWatt

- 3Phases/partitions

| Partitions                         | Availability | # di Racks | Power  |

|------------------------------------|--------------|------------|--------|

| A1 – Broadwell (2.1PFlops)         | April2016    | 25         | 700KW  |

| A2 - Knight Landing (11<br>Pflops) | July 2016    | 50         | 1300KW |

| A3 – Skylake (7PFlops)             | June 2017    | 30         | 1000KW |

#### 2019-2020 : 50PFlops

- > 50PFlop

- 130 racks

- 3.2 MWatt

| Partitions                           | Availability | # di Racks | Power  |

|--------------------------------------|--------------|------------|--------|

| Non conventional proc.<br>(40PFlops) | 2019         | 80         | 2400KW |

| Standard procs- (10PFlops)           | 2019         | 28         | 800KW  |

| 1.2Mwatt | 2.4Mwatt | 2.3Mwatt | 2.3Mwatt | 3.2Mwatt |

|----------|----------|----------|----------|----------|

| 50 rack  | 120 rack | 120 rack | 120 rack | 150 rack |

| 100mq    | 240mq    | 240mq    | 240mq    | 300mq    |

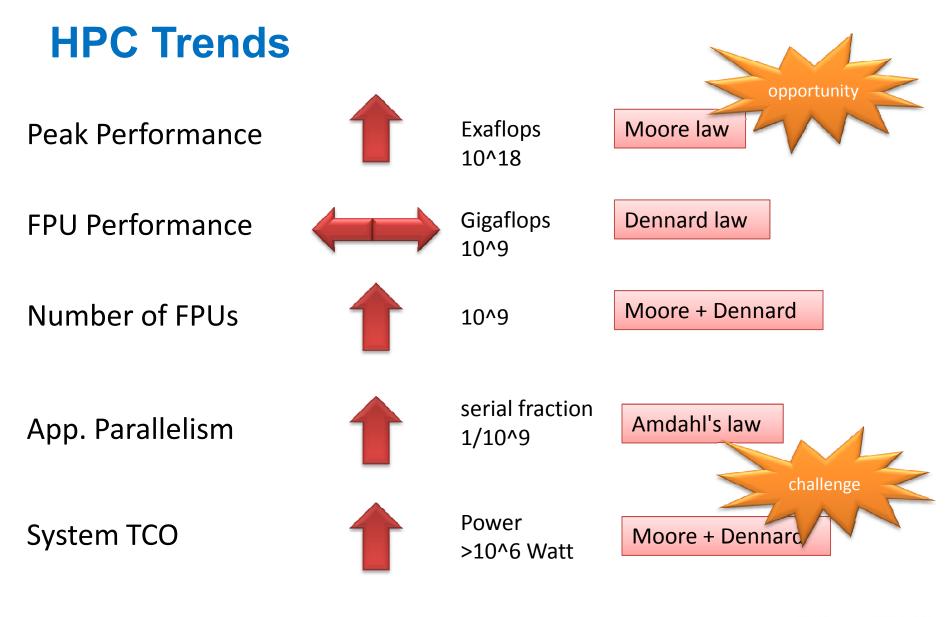

### **HPC Trends**

## Dennard scaling law (downscaling)

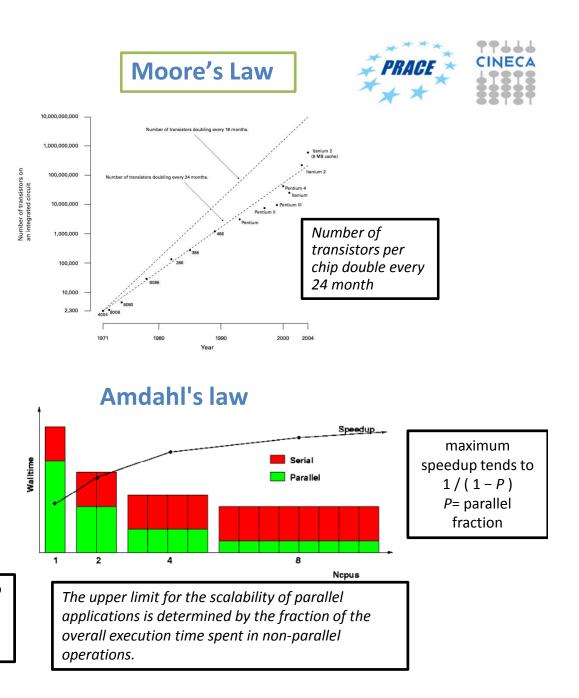

The core frequency and performance do not grow following the Moore's law any longer

Increase the number of cores to maintain the architectures evolution on the Moore's law

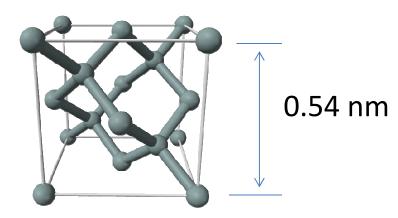

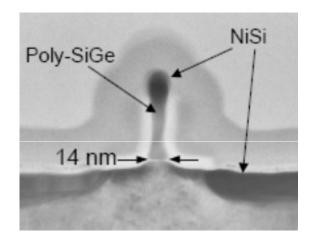

## The silicon lattice

Si lattice

50 atoms!

#### **Oh-oh!** Huston!

### **Energy trends**

Compute Power

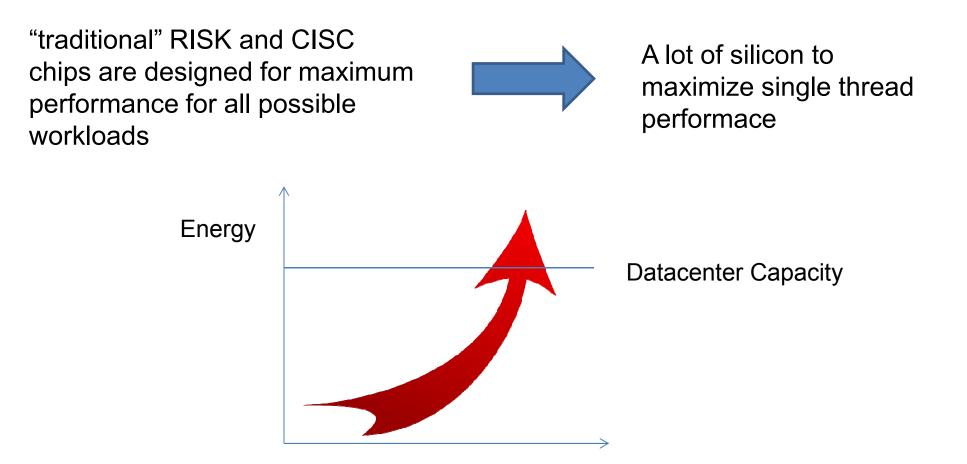

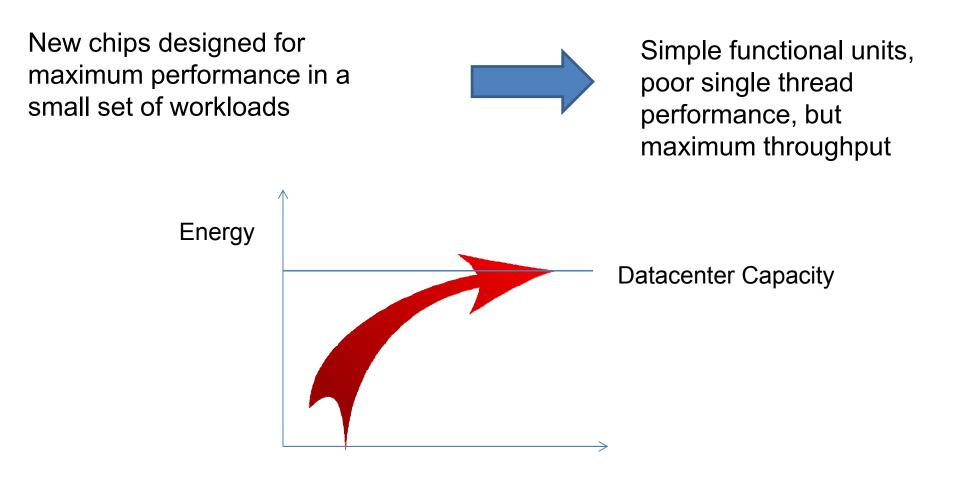

### **Change of paradigm**

Compute Power

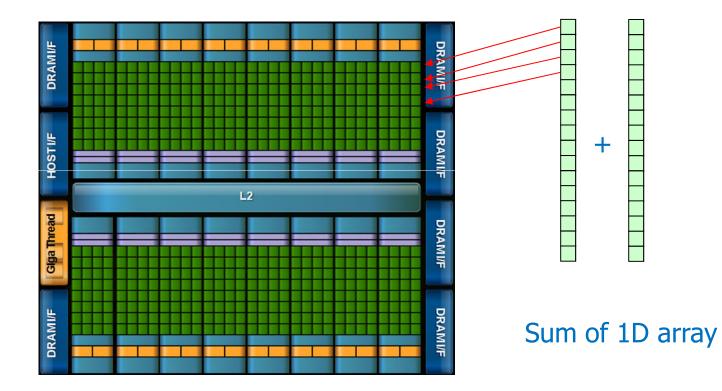

## Accelerator/GPGPU

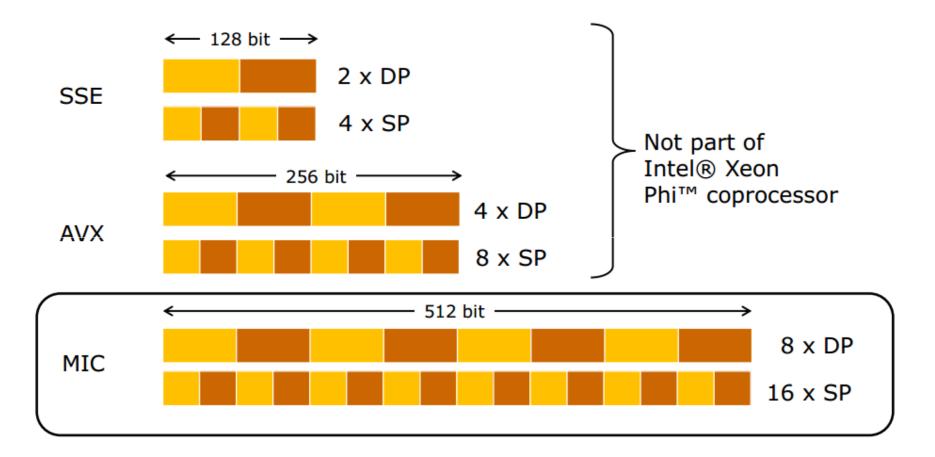

### **Intel Vector Units**

New AVX512 -> 2 vector FPU/core -> 32Flop/Clk

## GPU vs MIC

- At low level (innermost loops) in both cases we need to expose an high level of parallelism

- At high level GPUs push for offloading programming model, with "micro"-tasking

- At high level MIC push for a task level programming model, with task nesting

- Both need much less synchronizations at MPI level

# **Applications Challenges**

•Programming model

•Scalability

•I/O, Resiliency/Fault tolerance

•Numerical stability

•Algorithms

•Energy Awareness/Efficiency